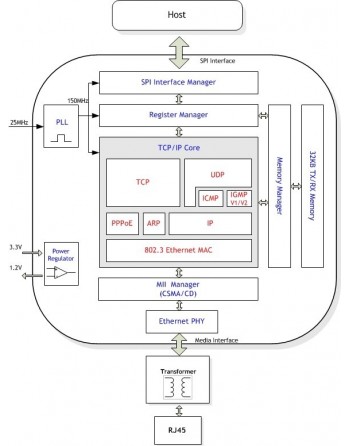

W5500 suits users in need of stable internet connectivity best, using a single chip to implement TCP/IP Stack, 10/100 Ethernet MAC and PHY. Hardwired TCP/IP stack supports TCP, UDP, IPv4, ICMP, ARP, IGMP, and PPPoE, …, which has been proven through various applications over many years. W5500 uses a 32Kbytes internal buffer as its data communication memory.

By using W5500, users can implement the Ethernet application they need by using a simple socket program instead of handling a complex Ethernet Controller. It is possible to use 8 independent hardware sockets simultaneously. SPI (Serial Peripheral Interface) is provided for easy integration with the external MCU. The W5500 SPI supports 80 MHz speed and the new efficient SPI protocol, so users can implement high speed network communication. In order to reduce power consumption of the system, W5500 provides WOL (Wake on LAN) and a power down mode.

Features

- Supports following Hardwired TCP/IP Protocols : TCP, UDP, ICMP, IPv4, ARP, IGMP, PPPoE

- Supports 8 independent sockets simultaneously

- Supports Power down mode

- Supports Wake on LAN over UDP

- Supports High Speed Serial Peripheral Interface(SPI MODE 0, 3)

- Internal 32Kbytes Memory for Tx/Rx Buffers

- 10BaseT/100BaseTX Ethernet PHY embedded

- Support Auto Negotiation (Full and half duplex, 10 and 100-based)

- Not support IP Fragmentation

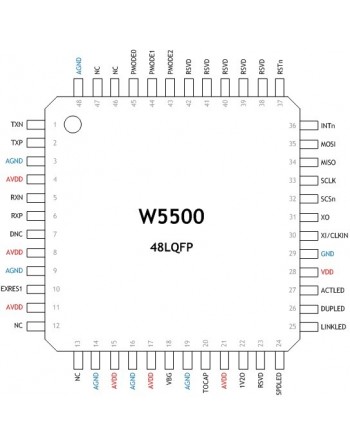

- 3.3V operation with 5V I/O signal tolerance

- LED outputs (Full/Half duplex, Link, Speed, Active)

- 48 Pin LQFP Lead-Free Package (7x7mm, 0.5mm pitch)

Download

Datasheet

Limitation Note

ioLibrary (Driver)

Application Note

W5500 IPRAW Mode v1.1.0

W5500 PPPoE v1.0.1

Migration Guide: W5200 to W5500

Hardware Design Guide

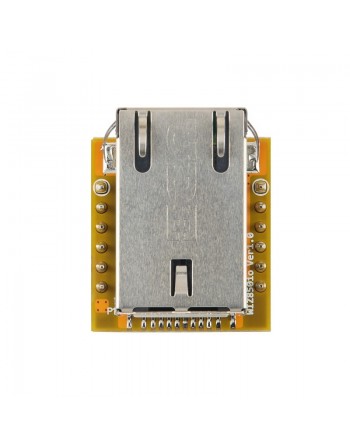

External Transformer Type

RJ45 Connector with Transformer Type