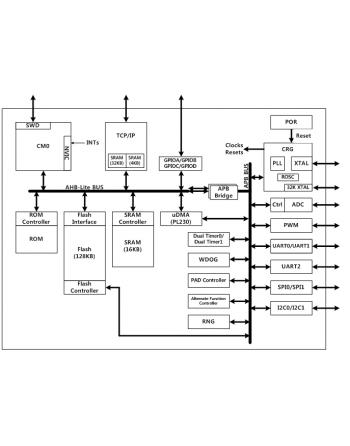

IOP (Internet Offload Processor) W7500 是一款集成了 ARM Cortex-M0、128KB Flash 和硬連線 TCP/IP 內核的單芯片解決方案,適用於各種嵌入式應用平台,特別是需要“物聯網”。

2,500片/盒

TCP/IP 核心是經過市場驗證的硬件 TCP/IP 協議棧,帶有集成的以太網 MAC。硬件 TCP/IP 協議棧支持 TCP、UDP、IPv4、ICMP、ARP、IGMP 和 PPPoE,已在各種應用中使用多年。 W7500P 最適合需要 Internet 連接進行應用程序的用戶。

主要特徵

硬件 TCP/IP 核心

記憶體

時鐘、復位和電源管理

模數轉換器

DMA

GPIO 通用輸入輸出接口

調試模式

定時器/PWM

通訊接口

加密

封裝 : 64 TQFP (7×7 mm)

下載

IOP (Internet Offload Processor) W7500P 是集成了 ARM Cortex-M0、128KB Flash 和硬件 TCP/IP 內核和 PHY 的單芯片解決方案,適用於各種嵌入式應用平台,特別是需要“物聯網”。

2,500片/盒